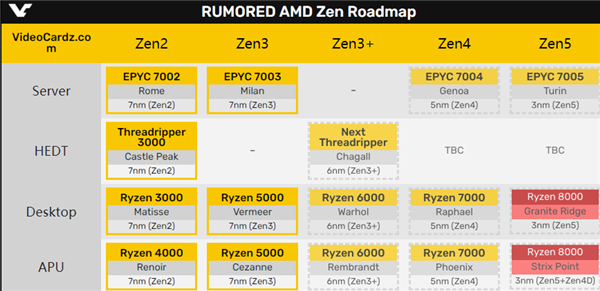

蘇媽近日確認,5nm Zen4架構的Ryzen、EYPC處理器都將在明年登場,而在那之前,今年底不是Zen3+,就是Zen3穿馬甲。

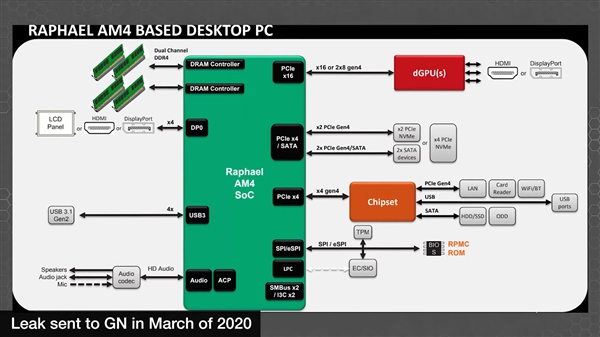

外媒披露了一份AMD內部資料,時間是今年3月,列出了Zen4架構首款Ryzen 處理器“Raphael”(拉斐爾)的詳細情況,預計將會命名為Ryzen 7000系列。

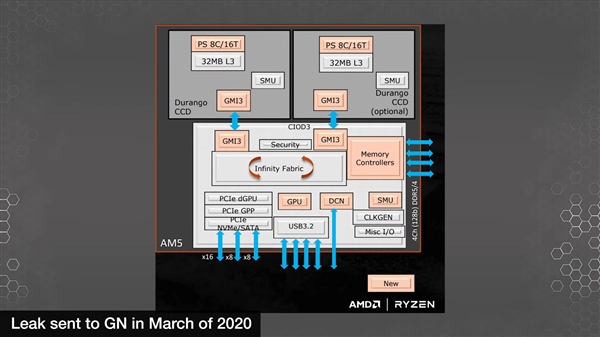

它依然採用chiplest小晶片設計,計算核心與輸入輸出分離,分別叫做CCD、CIOD3,製造工藝分別是台積電N5 5nm、N7 7nm。

CCD部分代號“Durango”,每個最多8核心16執行緒、32MB三級快取,和現在的Zen3完全一樣,兩個組成最多16核心32執行緒、64MB三級快取。

之前有消息稱AMD在測試24核心型號,但是否推出還要看各方面情況。

同時入門級型號會集成GPU,終於升級到RDNA2架構,但具體規格配置待定。

整體採用AM5封裝介面,熱設計功耗方面中高階桌上型型號45-105W,比現在下探20W,筆電型號35-65W,比現在上探20W。

另一張幻燈展示了Raphael處理器的內部結構。

CCD、CIOD3之間通過新的GMI3匯流排相互連接,後者集成新的記憶體控制器(DDR5)、GPU圖形核心。

以往的銳龍APU都是單晶片設計,這將是第一次採用chiplet多晶片設計。

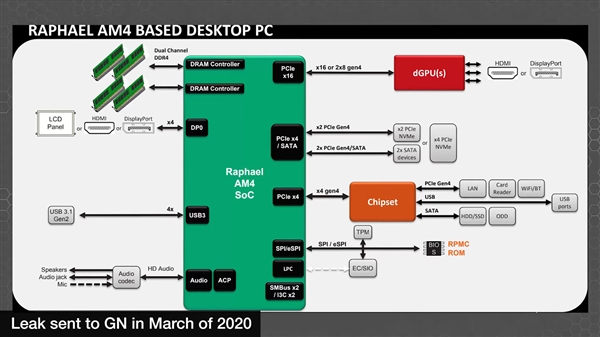

最後是Raphael平臺架構圖,確認繼續支持PCIe 4.0,通道數量從24條增加到28條,其中16條分給獨立顯卡、4條連接PCIe/SATA SSD、4條連接晶片組(600系列)之後再擴展支援網卡、讀卡器、Wi-Fi(藍牙)、USB、硬碟、光碟機等等。

再往後的Zen5架構的Ryzen 8000系列,也有消息傳出,台積電3nm工藝,同時集成Zen4D組成大小核心混合架構,最多8+4的組合,並有新的快取體系、記憶體子系統。